回路図から入力インピーダンスを求める 実は、先ほどの回路、フタを開けてみると、次図のような配線になっていました。さて、回路から入力インピーダンスを求めてみましょう。 内部の回路 C点のDC電圧は0Vつまり、アースです。Mar 22, 19 · 三菱電機製シーケンサFXシリーズにおける「接点形比較」命令とは、 定数やデバイスの値を比較して条件に合致していれば接点がONする ラダープログラム命令です。 接点形比較を用いることで、データレジスタやファイルレジスタといったワードデバイスの 大小を比較して条件分岐 したり、 特定のデバイス値であるか判断 して処理を実行することができますMar 10, 08 · 比較の種類は、4つの項目に分かれています。 Differences associated with Components コンポーネントレベルで実行される比較(例えば、回路図やPCBドキュメントで異なったデジグネータを持つコンポーネントの検知)。

通过比较视觉和听觉系统的回路构建策略来理解神经发育 细胞 神经元 毛细胞 耳蜗 感受器 网易订阅

比較回路 応用例

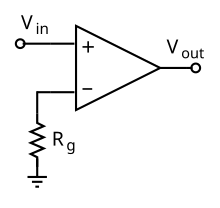

比較回路 応用例-(a) 非反転増幅回路を作成する.ただし,R 1 =12kΩ,R 2 =18kΩとする.電圧利得の実測値(v 2 /v 1 )と理論値(1R 2 /R 1 )を比較する. (b) 入力電圧と出力電圧をスケッチし,同相になっていること(回路規模)と性能の関係が重視され,一般に回路規模が コンパクトで変換時間が高速な逐次比較型を搭載する傾向 があります.逐次比較型は,da(ディジタルアナログ) 変換回路と比較回路,ad変換結果レジスタ,ad制御

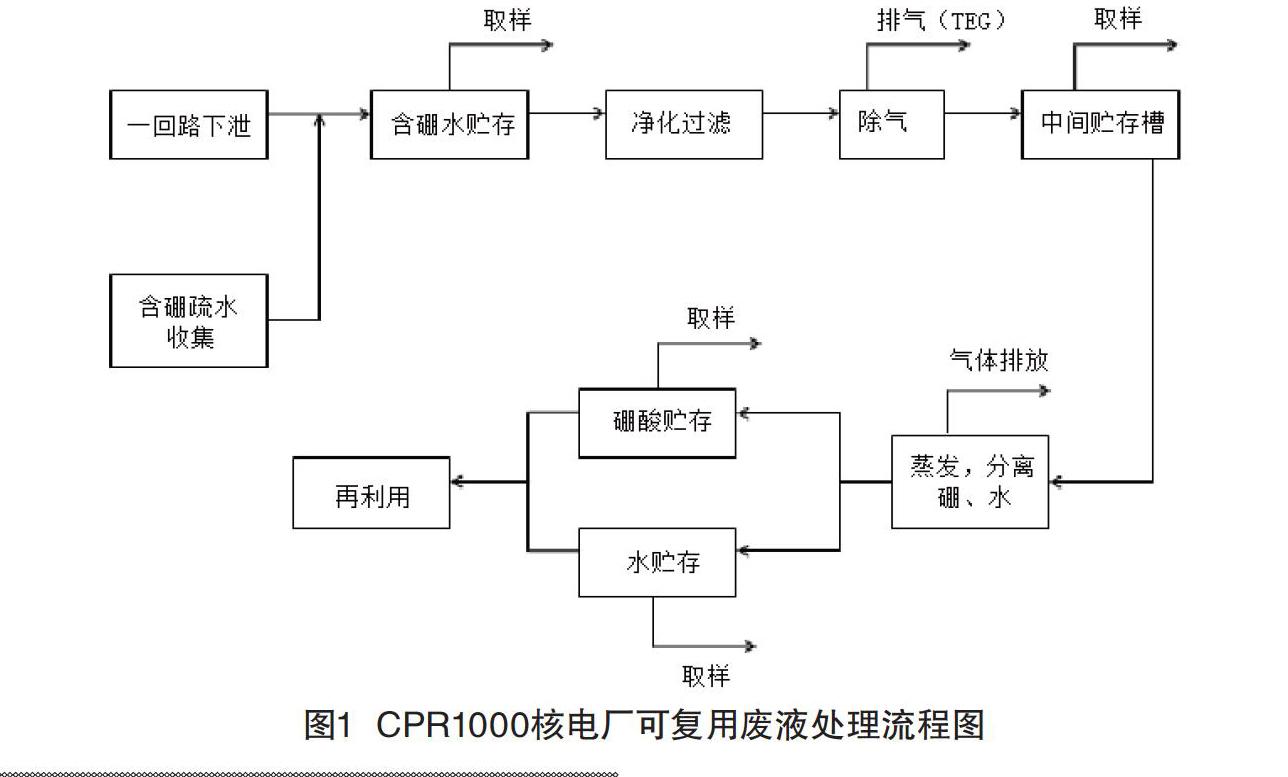

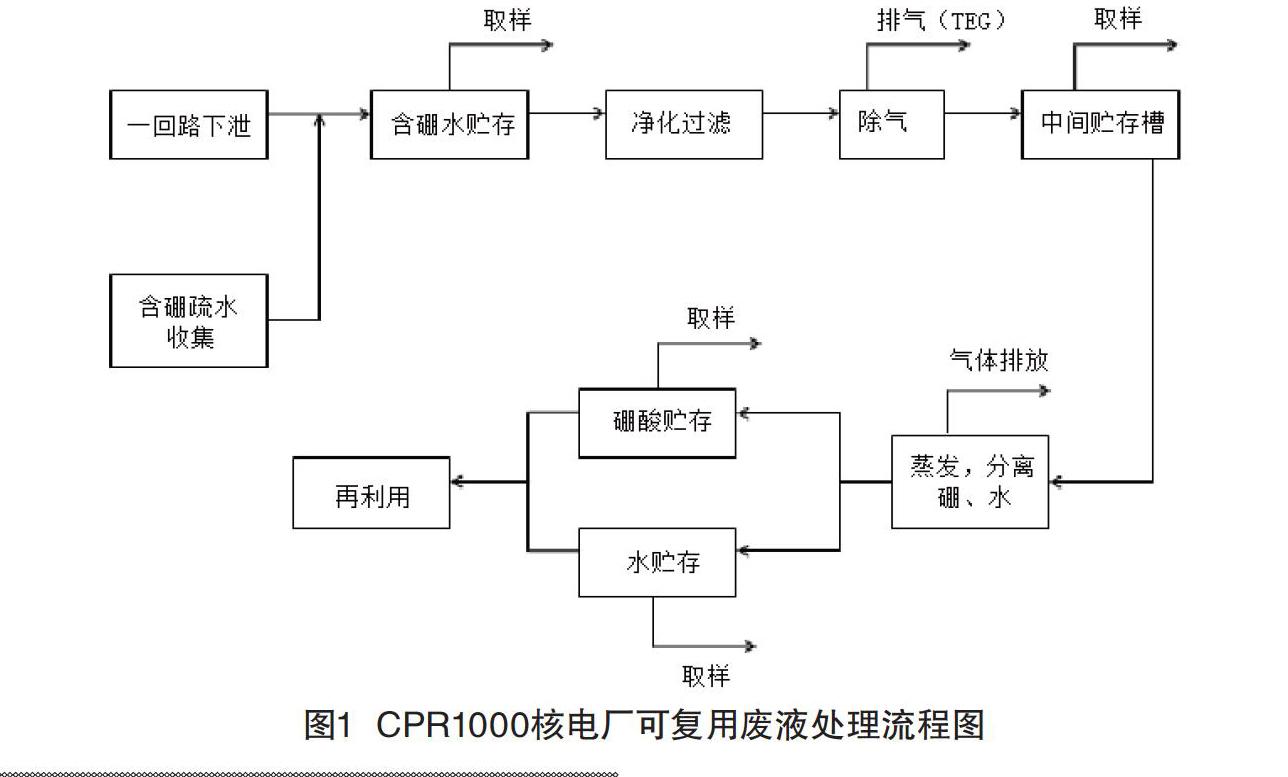

Ap1000与cpr1000放射性废液处理系统的比较研究 参考网

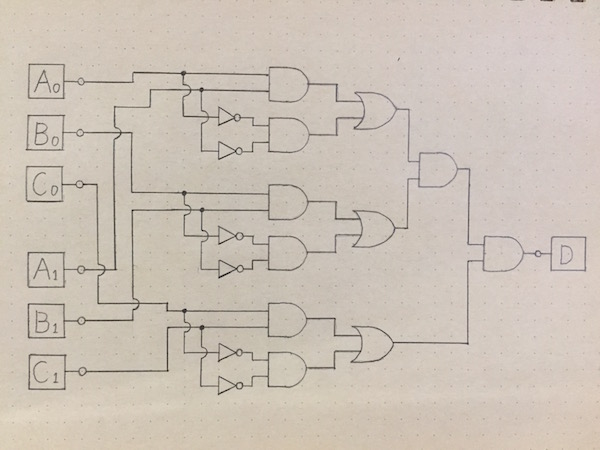

比較回路を、第1段目比較回路部と第2段目比較回路部の2段構成とする。 例文帳に追加 The comparator circuit is configured of twostage of a first stage comparator circuit section and a second stage comparator circuit section 特許庁ネット比較が自動で出来れば この作業は軽減され 又安心も出来ます ② 基板の改版時 前回作成のネットリストと 変更回路図ネットリストとの比較 ③ 回路図からのネットリストと 基板CADからのネットリスト との比較電子工学における コンパレータ (comparator) とは、二つの電圧または電流を比較し、どちらが大きいかで出力が切り替わる素子である。 より一般に、二つのデータを比較する装置にも使われる用語である。 次の図のような、モデル的なオペアンプに負帰還をかけていない状態として

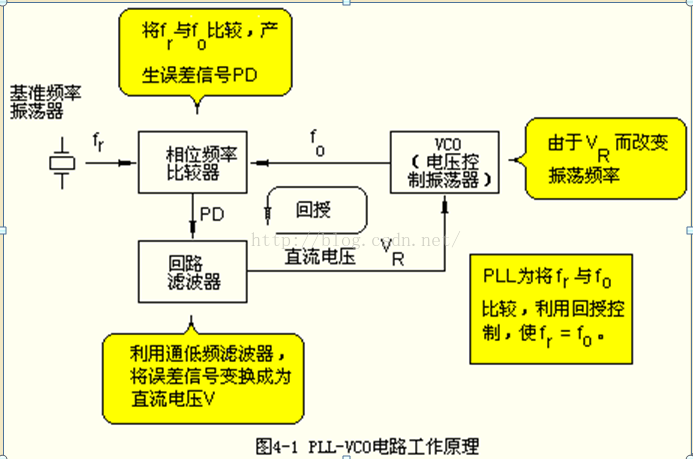

オペアンプ 回路構成 オペアンプは一般的に入力段、利得段、出力段の3段階内部回路構成となっています。 入力段は差動増幅段で構成されており、2つの端子間の差電圧を増幅します。 次に、入力段の差動増幅回路のみでは利得が不十分であるため、利得段によりさらにオペアンプの開放利得特集 ホントに使える電子回路教科書 図6-1(a)(b)に示すのは,コンパレータ回路です. 日本語では電圧比較器と言います.入力電圧Vinと 基準電圧Vrefを比較して出力状態を変えます. 反転型コンパレータでは,入力電圧が基準電圧よあらまし 2つの信号間の位相差に応じた電圧を出力する 位相比較器 は、現在では 位相周波数比較器 (Phase Frequency Comparator) と 呼ばれている回路方式の デジタル型比較器が多く用いられている。

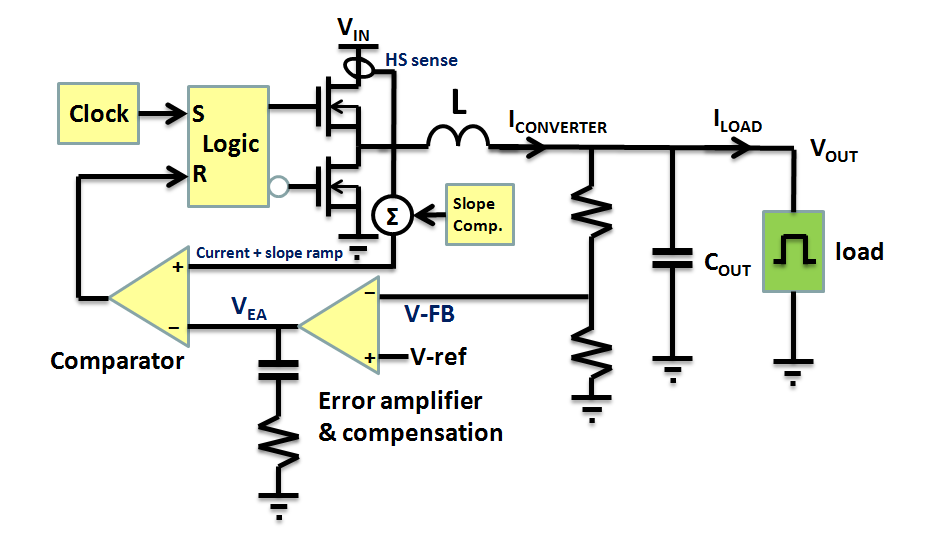

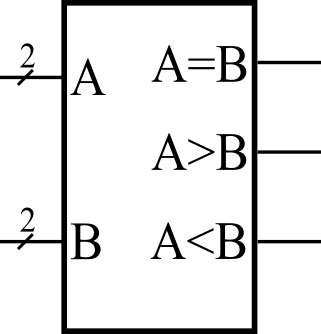

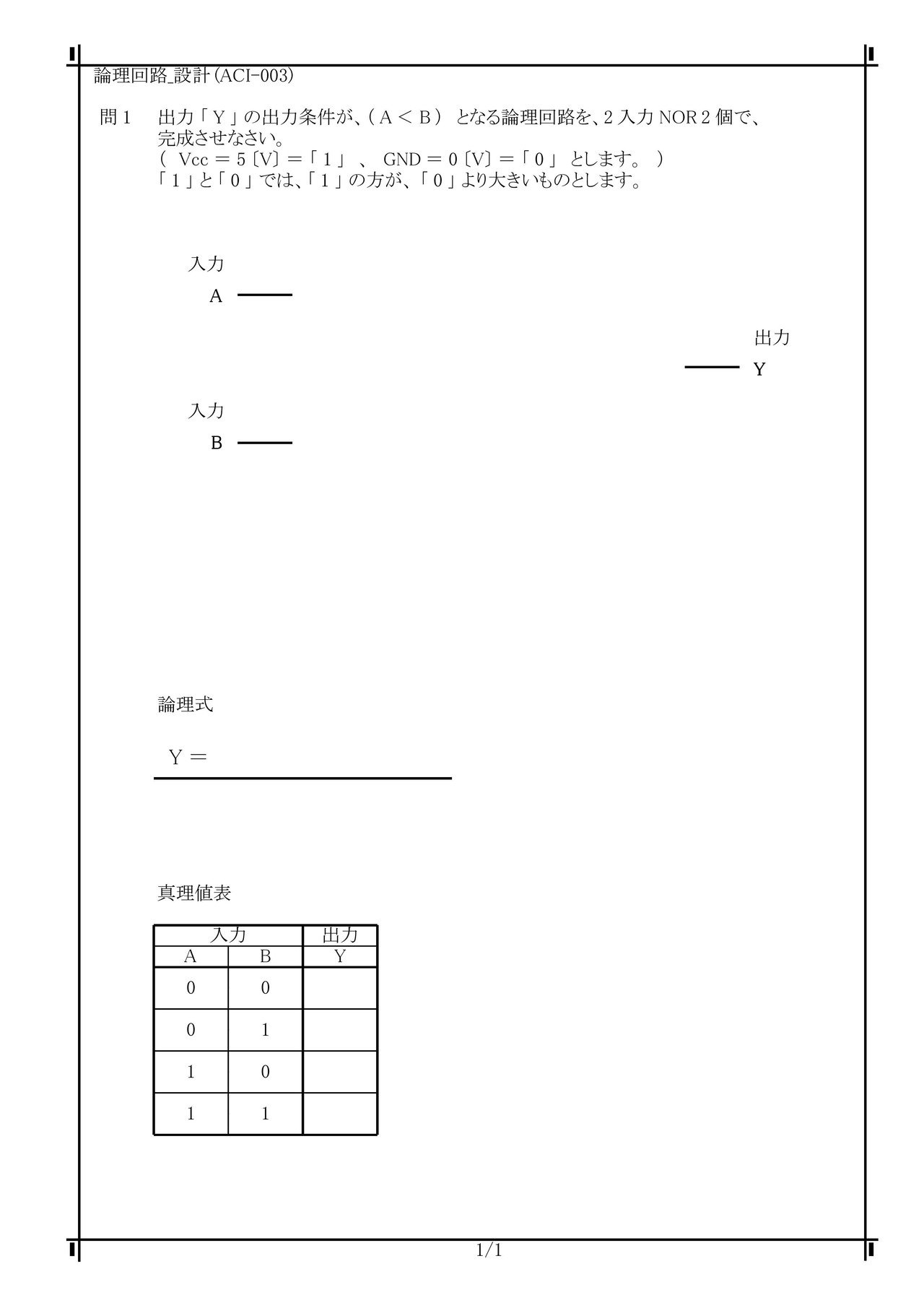

Jun 08, 12 · 前回はメジャーなコンバータ素子回路の特長、そしてその使い方の基本として、d/aコンバータを紹介しました。並列比較形 ad コンバータは、回路規模が大きいことが欠点ですが、最近の lsi の進歩によって、回路規模の大きさは、問題では無くなっています。 図 6435 並列比較形 ad コンバータ比較器(comparator) 入力の大小を比較する Z X X の方が大きい Z Y Y の方が大きい Z eq X とY が同じ • 2入力3出力 –入力 X,Y –出力 Z X,Z Y,Z eq Comp (X,Y) {if (X >Y) Z X = true;

环回路由 百度文库

回路电流和节点电压法 用回路电流法或者节点电压法解电路分析题 急求 5分 三人行教育网 Www 3rxing Org

比較回路というのは2つの入力信号が同じであれば「1」を出力する回路のことで、これも「 not 回路」「 or 回路」「 and 回路」の組合せで作ることができます。構造は以下のようになっています。この回路は、シュミット回路とか、ヒステリシス回路とも呼ばれています。 基本的な回路構成は下図のようにし、基準電圧Etが比較の基準になり ます。 この回路では、出力電圧のR2とR3による分圧した電圧がヒステリシスとElse Z eq = true;}

4 組合せ回路 Digital Electronic Circuits 1 0 ドキュメント

增强回路 值得 也需要用一辈子构建 知乎

CMOS比較回路(1)4ビット大小比較回路 CMOS Comparator Circuits (1) 4bit comparator circuits 波多野 裕*、 横井 和輝** Hiroshi HATANO and Kazuki YOKOI Abstract A 4bit CMOS digital comparator circuit has been successfully designed and fabricated using a double polysilicon and double metal 12 jtm CMOS technologyまずは、複数の入力信号の大小を比較し、その結果を出力する機能を持った回路である「 比較回路 (comparator)」について見てみることにしよう。 比較回路は二つ以上の多入力だが、今回は最も簡単な「2入力・3出力」について扱う。 ・比較回路 下に比較回路の論理式、真理値表、論理記号についてそれぞれ示した。 3出力のX、Y、Zは、それぞれ"A>B"、"A=B"、"ASep 08, · コンパレータは英語の compare「比較する」 を語源とするように、 比較器・あるいは比較回路 などと称されることがあります。 ディスクリート半導体の一種ですが、各種回路とパッケージングされて IC として用いられることが一般的で、冒頭でも述べたように多くのアナログ回路に搭載されています。

コンパレータ 比較器 電子工作で覚える 電子回路

12星座的脑回路是怎样的构造 青岛心理咨询 心医觉民心理工作室

す.opアンプと特性を比較すると,一般にオフセッ ト電圧やバイアス電流などの直流特性は悪いですが, 動作スピードは非常に高速です.出力回路は,オープ ン・コレクタ(オープン・ドレイン含む)か,ロジック icの出力と同等(ttl,cmosなど)です.複雑な回路をより簡単な回路(設計済み)の 組み合わせで作る • 設計が簡単になる • 回路の量産化で製作コスト削減 回路のモジュール化 回路全体を1つのゲートとみなす 例 比較器 Zeq X Y ZX ZY Comp Comp Zeq X Y ZX ZY モジュール化 大小比較 3桁の数の大小比較( 例Aug 27, 19 · 直列回路と並列回路 回路には、直列と並列があります。おそらく、知っている方が大半かと思いますが、その"違い"を見分けたい場合、どんな

5 ビットコンパレータ回路

怎样配制配电箱 时习社区

制御回路は、 (a) Vi ≧ Vo であれば bn1 を1のままにし、次の下位ビット bn2 を1に設定する。 (b) Vi < Vo であれば bn1 を0に変更して bn2 を1に設定する。 この状態で再び Vi と Vo を比較して、その結果を同様に制御回路にフィードバックする。 このようにD/A変換器を用いて2分検索を行う。 以後、この動作を繰り返すことでアナログ量をディジタル量に変換している(57)要約 目的 本発明は比較回路に関し、ヒステリシス電圧 の精度を容易に高められることを目的とする。 構成 差動対トランジスタ21は、エミッタ面積比 が1対3に設定されており、共通エミッタに電流源30 が接続されており、夫々のベースに、V Z と検出対象電 圧Vccを分圧したV S が図4 1ビットの比較回路 もし、nビットの一致比較を行ないたければ、各ビットの比較の積をとって となるので、図5のような回路が得られます。 file//H\サーバー\lachesis\Manual\Logic\digital2html 5/ ページ

比較回路 コンピュータの仕組み 研究開発 相楽製作所

Tq 100型同期继电器 上海约瑟电器有限公司

電子回路 コンパレータ(比較器とも言う)は、2つの電圧を比較するために用いられます。 オペアンプを用いてコンパレータ(比較器)を実現します。 電子回路設計 入門サイト 電子回路設計 入門サイト トップページ サイトマップ&What's new!Adc 基本形3(逐次比較<sar>型) adc逐次比較型は、標本化したアナログ信号と、dac (d/aコンバータ) の出力が一致するようにmsb (最上位ビット) から順に逐次比較をしていきます。 18ビット程度までの高分解能が実現可能です。 変換のためにクロックサイクルが必要なため、変換速度は比較回路を、第1段目比較回路部と第2段目比較回路部の2段構成とする。 例文帳に追加 The comparator circuit is configured of twostage of a first stage comparator circuit section and a second stage comparator circuit section 特許庁

继电保护及二次回路 国网教材 电流

知识对比 升降压与cuk斩波电路模块比较分析 电路保护 电子元件技术网

応用2:比較回路 大きさの比較回路(1ビット) 2進数の大きさを比較する回路を作成します。まず、一桁の比較回路を考えます。a と bを比較し、aがbより小さいときl、等しいときe、大きいとき g、を1とします。 e=a・b は間違いです。May 08, 12 · この回路構成は、電圧比較用のトランジスタの接続を入れ替えると出力の動作を変えられるという利点もある。 pnp型とnpn型を1個ずつ、合計2個のトランジスタを用いたコンパレータの回路例を図1、図2に示す。図1は基準電圧よりも低レベルの入力、図2は高レベルの入力を検出するコンパレータの構成例である。Jan 30, 19 · 他の回路シミュレータとの比較は? Spiceman / 0322 スポンサーリンク 当記事では、数あるアナログ回路シミュレータと比較して、LTspiceがなぜおすすめなのかについて詳しく説明します。 LTspiceは、無償かつ回路規模が無制限で使用できる上に、他社のSPICEモデルの利用が可能だったり、解説情報が多かったりと、大変使い勝手が良いのです。 回路

将运算放大器用作比较器时需要注意的事项 电子发烧友网

Tq 100型同期继电器 上海约瑟电器有限公司

2 組合せ回路の設計 加算器(1) 2進法 桁上げ 28) 11 17 10進法 通常の 代数 11=10 ) 011=10Else if (Y >X) Z Y = true;Feb 09, 17 · Logisimで組み合わせ回路(Combinational Logic)の比較回路(Comparatorコンパレータ)を学んでいきます。比較回路は、単純に2つの入力を比較して、その状態を出力します。 ひと桁の二進数の入力Aを考えると0か1です。 入力A 0 1

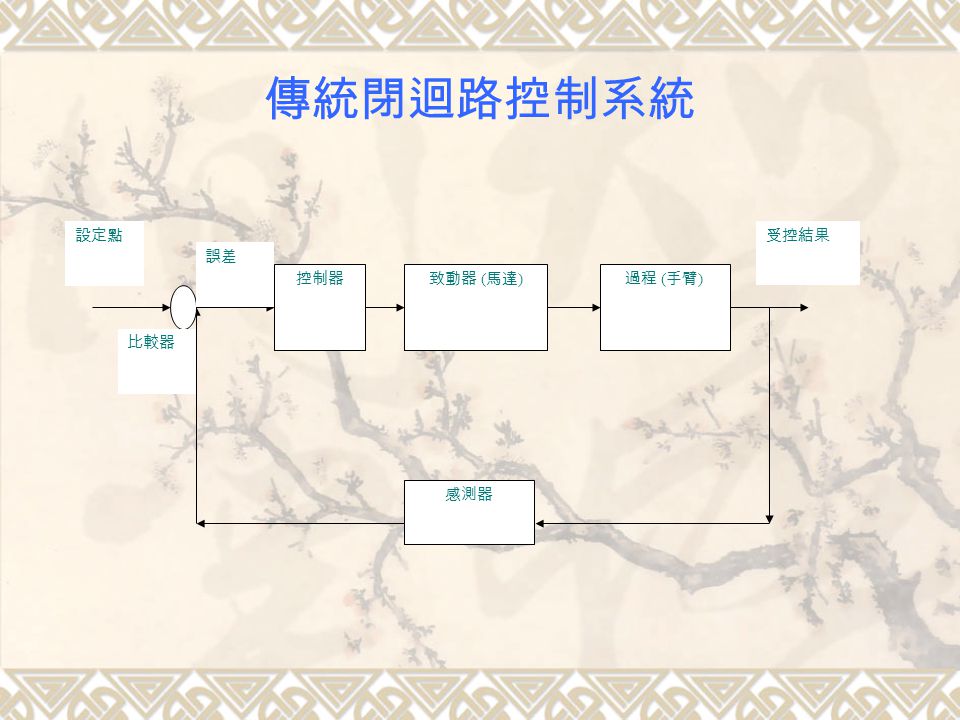

傳統閉迴路控制系統控制器致動器 馬達 過程 手臂 感測器設定點受控結果誤差比較器 Ppt Katebasma

求助一下比较器的问题 编程语言 Csdn问答

比較器とは入力された 2 個の数 a, b について、a が大きいか、等しいか、 b が大きいかを判定する回路である。 まず 1 ビットの数の大小を判定する回路を構成し、その後複数ビットに拡張する。Oct 12, · 比較回路(コンパレータ)は、入力された数値を比較して、一致や大小を判定する回路です。 図1は、2つの2ビットの入力信号a,bを比較する回路のシンボル図です。表1は、図1の比較回路の大小比較の論理回路 まず,2入力 , の大小関係を比較する論理回路として,図41のような回路を考案した.次に,XNOR回路用にIC4077を,NOR回路用にIC4001をそれぞれ用いて,ブレッドボード上で図41の回路を作成した.

电流信号在控制回路中的作用 大大通

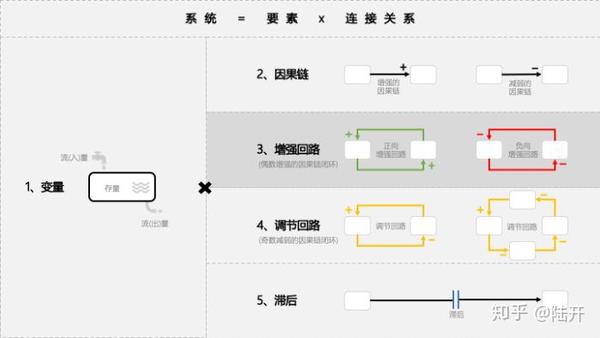

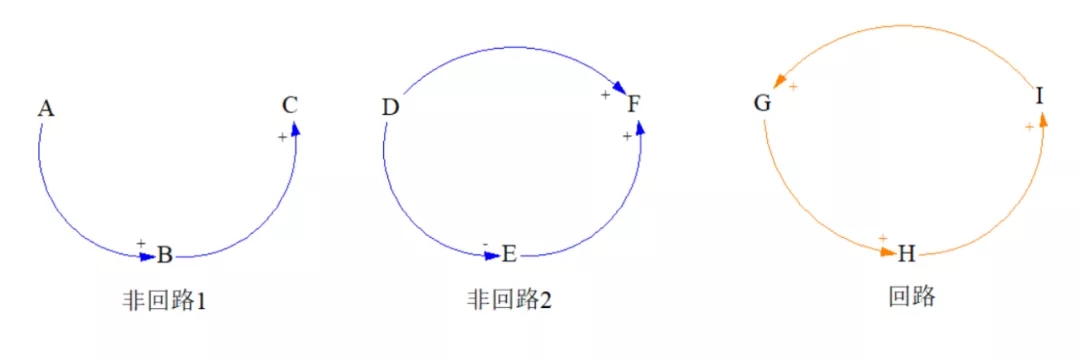

一文搞懂因果回路图 掌握系统思考关键工具 安晓辉生涯 微信公众号文章阅读 Wemp

nビット比較回路

一文搞懂因果回路图 掌握系统思考关键工具 Mba智库资讯

九九厕所偷拍精品视频 沟厕欣赏女尿高清

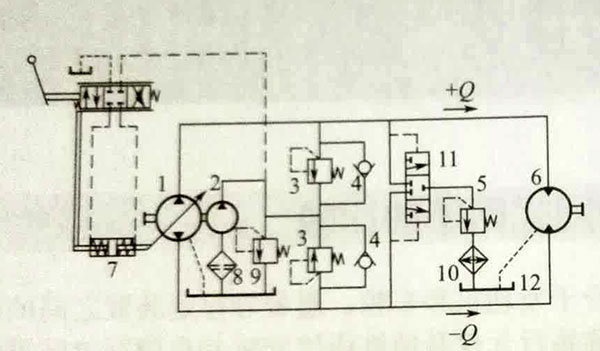

平衡回路的功用以及其常见的分类类型 Parker液压指定授权代理商 Parker派克 Parker代理 Parker液压 Parker派克油缸 Parker派克液压泵 Parker派克阀 Parker派克管件 Parker派克马达 Parker派克液压马达 派克汉尼汾 上海德托流体技术有限公司

Adalm00實驗 運算放大器作為比較器 Compotech Asia

继电保护及二次回路 下载 Word模板 爱问共享资料

最新消息 得邁斯科技 Fluke校正器入口網站 Fluke Ametek Ircon Ca 溫度校正 壓力校正 電量校正 程控校正 迴路校正 紅外線溫度計 熱像儀 雷射修阻機

アナログとディジタル

1

插座迴路連接工法有哪些 怎麼接比較安全 立宇生活科技

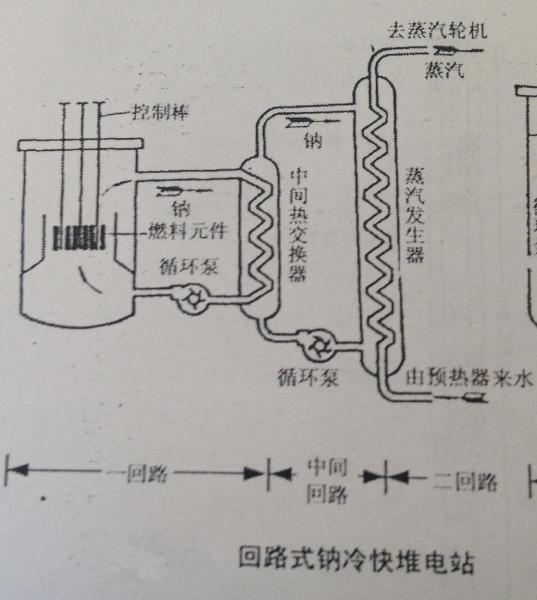

快中子堆 搜狗百科

蜂回路转手游 蜂回路转最强大脑游戏下载v1 0安卓版 西西软件下载

Uci研究人员发布了有关神经回路图谱中病毒示踪剂的新指南 细胞

コンパレータ 比較器 電子工作で覚える 電子回路

論理ゲート ナノエレクトロニクス

Circuit Explanation For Ultrasonic Range Meter

Pgc結合位相反轉回路之一 Stein 大小聲 隨意窩xuite日誌

位相比較器 Phase Frequency Comparator の動作

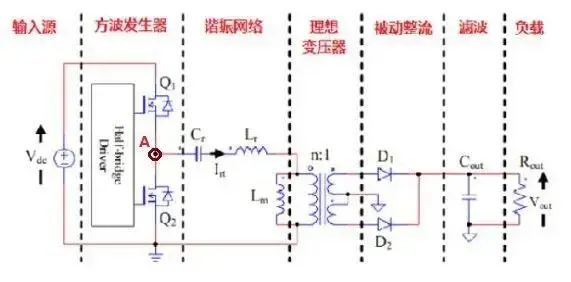

为什么我的llc变压器磁芯温度很高 Llc变压器设计经验4条 电源技术与新能源 面包板社区

比較回路 石丸技術士事務所 ディジタル技術資料

液壓基本迴路來實現了液壓系統中每個動作 你知道有哪些迴路嗎 每日頭條

知识对比 升降压与cuk斩波电路模块比较分析 电路保护 电子元件技术网

Ap1000与cpr1000放射性废液处理系统的比较研究 参考网

继电保护及二次回路 下载 Word模板 爱问共享资料

02 号 大小比較回路 Astamuse

02 号 大小比較回路 Astamuse

简单了解滤波 稳压 比较 运放电路 用户体验 Rohm技术社区

电源转换应用中数字反馈回路的好处是什么 电子发烧友网

1

家装电线回路如何划分才合理 诸暨网

实例分析 四个方面谈llc变压器设计经验 哔哩哔哩

欧拉回路 吹水小镇

实验课程 西安交通大学核安全与运行研究室 Nuclear Safety And Operation Lab Nusol

長模組上的採樣迴路阻抗 壹讀

Pid控制器 维基百科 自由的百科全书

什么是闭式回路液压系统用在哪些设备上

左家庄信息港

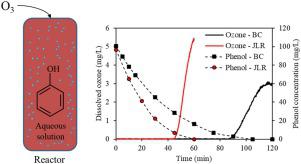

射流回路反应器和鼓泡塔中臭氧氧化去除苯酚的比较 Journal Of Environmental Chemical Engineering X Mol

電子迴路 Wikiwand

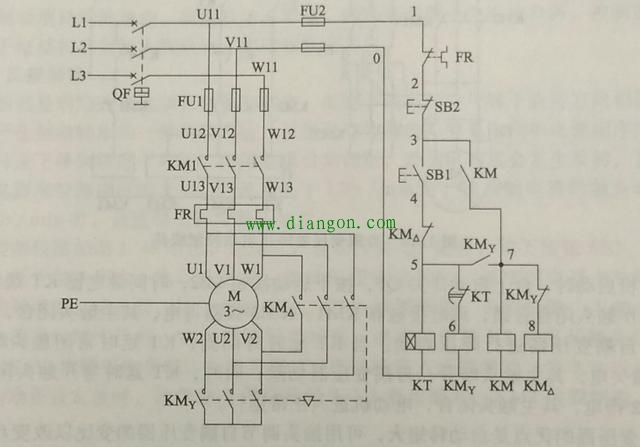

两种星三角启动电路比较 电动机 电工学习网

長模組上的採樣迴路阻抗 每日頭條

1

基本气动回路 Doc 十八文库

罗百辉的审定是我国立异型中小模具企业的渴望已进入了 井喷阶段 若单回路与另外一带电高压线有平行段时 亦应将另外一回路 停电久久九九久精品国产 临沂市航伯高温材料制造公司

过流自锁电路 Eda365电子论坛通信数码 人工智能 计算机 半导体 手机家电消费电子硬件门户网站

コンパレータ 比較器

晶体管放大电路三种组态的比较 腾讯视频

二次回路中的高压pt详细讲解 Eda365电子论坛通信数码 人工智能 计算机 半导体 手机家电消费电子硬件门户网站

插座迴路連接工法有哪些 怎麼接比較安全 立宇生活科技

1

Jpa 逐次比較型ad変換回路 Google Patents

通过比较视觉和听觉系统的回路构建策略来理解神经发育 细胞 神经元 毛细胞 耳蜗 感受器 网易订阅

闪之轨迹4核心回路室女怎么获得 核心回路处女强度分析 3dm单机

Circuit Explanation Of The Temperature Controller Of The Bending Apparatus

Logisimで比較回路 Comparator を学ぶ はじめてプログラム

Pcb布线12条规则 地线回路 屏蔽保护 串扰控制 电路图 面包板社区

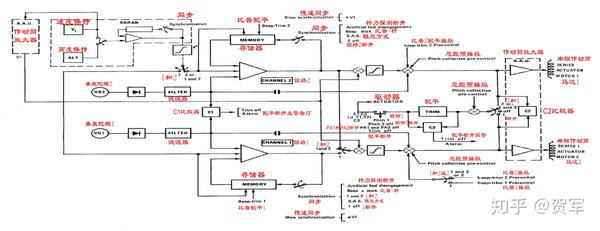

直升机自动驾驶仪系统ap155d自驾计算机工作原理与故障分析 3 知乎

コンパレータとは何か 回路の基本とコンパレータ回路の設計方法を勉強しよう ポイントはこれだ 比較 の原理 切り替わり動作 コンパレータ使用時における注意点 内部回路の簡単な設計 選定方法 とは など

增加放電迴路的rc複位電路圖 研發互助社區

Tms3f的模拟比较器学习 一 只要路是对的 就不害怕遥远 程序员宅基地 程序员宅基地

Woa1 逐次比較型ad変換回路 Google Patents

陶瓷电容器直流充放电的用途 网易订阅

コンピュータの仕組み 基本論理回路 機械語 Yokkunsの日記

Pll 锁相环 电路原理 Jason爱美腻的博客 Csdn博客

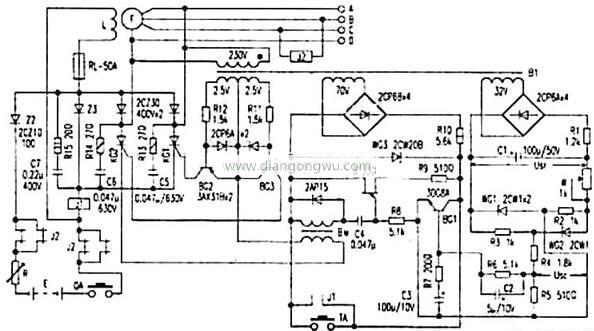

电流控制型开关电源的基本电路

數碼用戶迴路 Wikiwand

运算放大器 维基百科 自由的百科全书

家用电线用多少平方 电线线路安装应该设置多少回路

采用输出失调存储 Oos 的动态比较器问题 微波eda网

如何产生pwm信号 你知道吗 开源block

沈浸在音樂之中 貓窩工坊drc Do Something Rca訊號線ground Loop

電氣二次迴路圖學習有哪些竅門 雪花新闻

31 开关电源 Ac Dc转换器 的电路方式 Chip1stop 电子元器件 半导体的销售网站

相位保护继电器接线图 第1页 图说健康

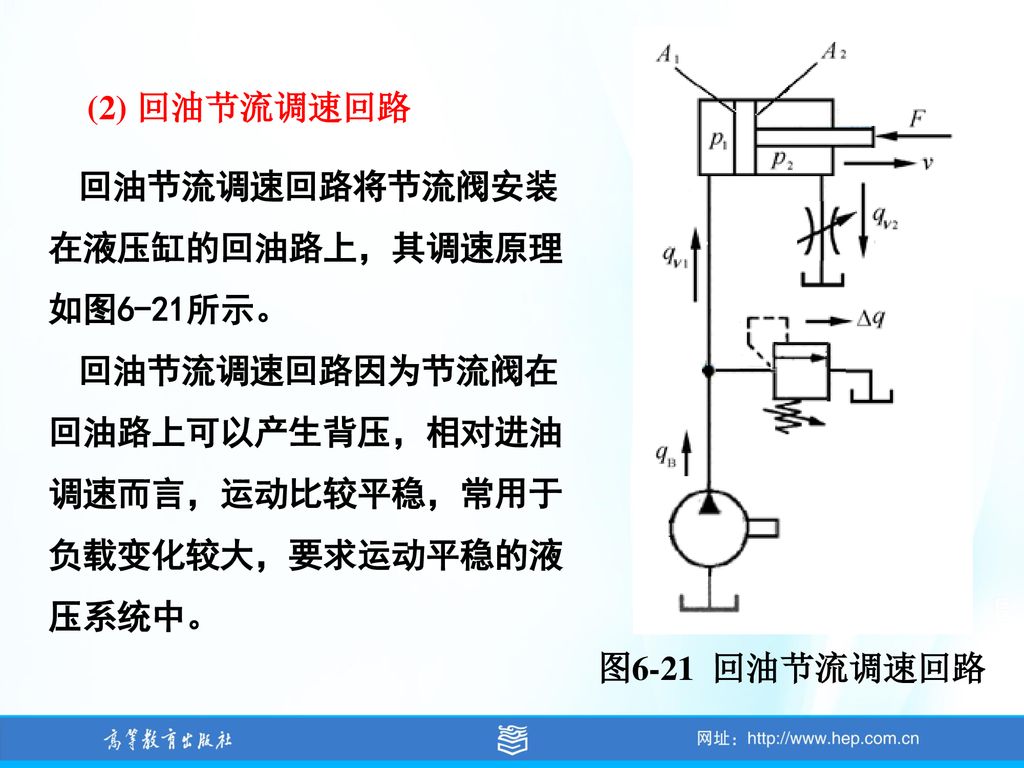

第六章液压系统的基本回路 Ppt Download

Aci 003 論理回路設計 論理回路 比較論理回路 2変数比較回路 ド モルガンの定理 ブール代数 真理値表 組合せ回路 組合せロジック に関する 問題と解答です Aci 003 電気の問題集研究所 Dmk Note

流量 液位回路pid抗积分饱和张建明浙江大学智能系统与控制研究所15 03 Ppt Download

Woa1 逐次比較型ad変換回路 Google Patents

挖掘機液壓系統的基本回路分析 華文網

有极性电解电容并联电路 Pcb抄板 Pcb打样 深圳市亿品优高精密电子有限公司官网

交流发电机励磁电压太低是什么问题 如何解决 交流发电机与直流发电机 电工基础 电工屋

一文搞懂因果回路图 掌握系统思考关键工具 Mba智库资讯

比较好的acs800变频器什么好 襄阳双龙威机电科技有限公司 创业服务

火線與零線的關係是什麼 爲什麼缺少零線就不行呢 雪花新闻

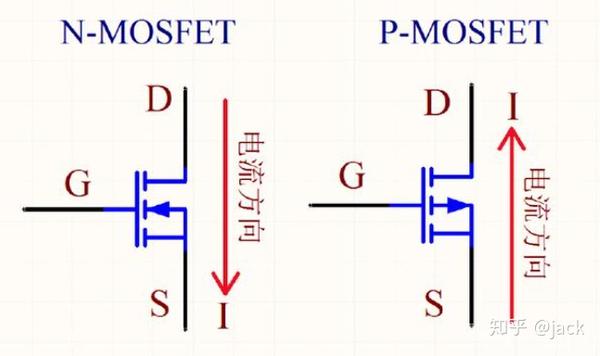

Mos管当开关控制时 一般用pmos做上管nmos做下管 知乎

挖掘機液壓系統的基本回路分析 華文網

0 件のコメント:

コメントを投稿